Category:D flip-flops

Subcategories

This category has the following 27 subcategories, out of 27 total.

4

- 4013 (CMOS) (17 F)

- 4076 (CMOS) (1 F)

- 40174 (CMOS) (1 F)

7

D

- Differential D latch (2 F)

E

- Earle latch (3 F)

G

- Gated D flip-flops (empty)

Media in category "D flip-flops"

The following 65 files are in this category, out of 65 total.

-

100ТМ131 Вента.jpg 894 × 874; 286 KB

-

2FF synchronizer.gif 644 × 766; 16 KB

-

Animation du fonctionnement d'une bascule.gif 289 × 286; 39 KB

-

Bascule - principe.png 289 × 286; 2 KB

-

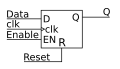

Bascule D avec entrée Reset, simplifiée.png 354 × 239; 8 KB

-

Bascule D avec entrée Reset.png 455 × 328; 11 KB

-

Bascule D en logique Dynamique, avec entrée Enable.png 853 × 332; 15 KB

-

Bascule D en logique dynamique.png 871 × 413; 16 KB

-

Bascule D fabriquée avec une bascule RS.png 606 × 203; 13 KB

-

BasculeD.png 102 × 105; 2 KB

-

Biestable D.PNG 281 × 153; 2 KB

-

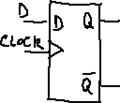

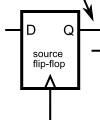

D F-F.png 108 × 118; 2 KB

-

D flip flop basic.png 431 × 173; 1 KB

-

D flip flop from nand gates.svg 468 × 248; 11 KB

-

D Flip-flop (Simple) Symbol.svg 100 × 100; 6 KB

-

D flipflop.jpg 346 × 244; 6 KB

-

D latch flip-flop circuit.png 311 × 178; 1 KB

-

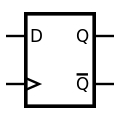

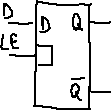

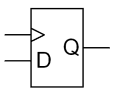

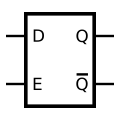

D latch flip-flop functional symbol.png 111 × 110; 466 bytes

-

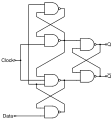

D master-slave flip-flop circuit.png 423 × 205; 2 KB

-

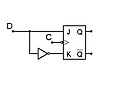

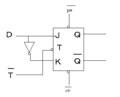

D master-slave flip-flop functional symbol.png 128 × 110; 528 bytes

-

D-E-T IEC-symbool.svg 100 × 100; 5 KB

-

D-FlipFlop (4-NAND, 1-NOT).PNG 960 × 400; 30 KB

-

D-flipflop-dontcare.svg 175 × 100; 8 KB

-

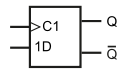

D-Latch IEC-symbool.svg 100 × 100; 5 KB

-

D-Latch.png 120 × 88; 2 KB

-

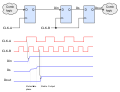

D-Type Flip-flop Diagram.svg 800 × 250; 32 KB

-

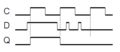

D-type flip-flop impulse diagram.png 572 × 231; 5 KB

-

D-Type Flip-flop with CE.svg 100 × 110; 1 KB

-

D-Type Flip-flop.svg 100 × 120; 8 KB

-

D-type Transparent Latch (NOR).svg 300 × 150; 21 KB

-

D-type transparent latch.png 375 × 200; 8 KB

-

D-Type Transparent Latch.svg 300 × 150; 20 KB

-

DMT D-FF Timing.png 378 × 165; 5 KB

-

DMT Pegel-D-FF Timing.png 378 × 165; 4 KB

-

DType Flip-flop FallingEdge.svg 100 × 120; 9 KB

-

Edge triggered D flip flop with set and reset.svg 601 × 700; 23 KB

-

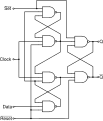

Edge triggered D flip flop.svg 512 × 548; 9 KB

-

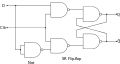

FF NAND-D.png 442 × 265; 16 KB

-

Flip-flop D enable input.svg 957 × 248; 7 KB

-

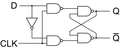

Flipflop D type.png 353 × 286; 728 bytes

-

Flipflopd edge-Triggered.svg 156 × 96; 6 KB

-

Flipflopd.png 120 × 99; 629 bytes

-

Flipflopd.svg 156 × 96; 6 KB

-

Gated D latch symbol.png 82 × 75; 422 bytes

-

GatedDLatch-lowres.gif 320 × 162; 1.06 MB

-

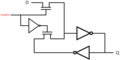

Implémentation conceptuelle d'une bascule D.png 386 × 177; 6 KB

-

Implémentation d'une bascule D différentielle.png 493 × 196; 7 KB

-

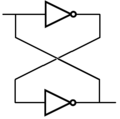

Inverter-ring flip-flop circuit.png 106 × 158; 754 bytes

-

Inverter-ring flip-flop transcharacteristic.png 195 × 175; 1 KB

-

Latchd.JPG 447 × 276; 10 KB

-

Launch Wave2.svg 100 × 120; 82 KB

-

Launch Wave3.svg 100 × 120; 303 KB

-

Metastability D-Flipflops-ru.svg 737 × 592; 7 KB

-

Metastability D-Flipflops.svg 730 × 560; 28 KB

-

Multiplexer-based latch (negative).svg 225 × 150; 11 KB

-

Multiplexer-based latch (positive).svg 225 × 150; 11 KB

-

Multiplexer-based latch using transmission gates.svg 300 × 175; 22 KB

-

Negative-edge triggered master slave D flip-flop.svg 512 × 205; 6 KB

-

Register from D flip flops.svg 471 × 229; 23 KB

-

Transparante latch IEC-symbool.png 163 × 119; 1,010 bytes

-

Transparent Latch Symbol.svg 100 × 100; 7 KB

-

Transparente latch als latch en poorten.png 235 × 157; 2 KB

-

Transparente latch.svg 1,482 × 409; 27 KB

-

USSR K176TM1.jpg 2,317 × 1,878; 332 KB